數(shù)字邏輯電路設(shè)計(jì)入門 基于74LS04反相器的Multisim仿真教程

在數(shù)字邏輯電路設(shè)計(jì)與學(xué)習(xí)過(guò)程中,仿真是一個(gè)至關(guān)重要的環(huán)節(jié)。它允許我們?cè)诓粚?shí)際搭建物理電路的情況下,驗(yàn)證設(shè)計(jì)的邏輯功能、分析時(shí)序并排查潛在問(wèn)題。本次教程將以最基礎(chǔ)、最常用的數(shù)字集成電路——74LS04六反相器(Hex Inverter)為例,詳細(xì)講解如何使用流行的電路仿真軟件(如NI Multisim)進(jìn)行仿真實(shí)驗(yàn),旨在為初學(xué)者提供一個(gè)清晰、實(shí)用的入門指南。

第一部分:認(rèn)識(shí)74LS04反相器

74LS04是TTL(晶體管-晶體管邏輯)系列的集成電路,內(nèi)部集成了六個(gè)相互獨(dú)立的反相器(非門)。其核心功能是邏輯取反:輸入高電平(邏輯1)時(shí),輸出低電平(邏輯0);輸入低電平(邏輯0)時(shí),輸出高電平(邏輯1)。

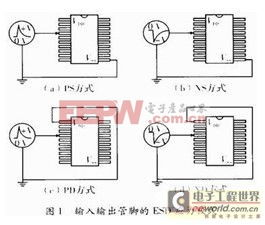

- 引腳圖:它是一個(gè)14引腳的雙列直插式封裝(DIP)芯片。通常,第7腳(GND)為接地端,第14腳(VCC)為電源正極(+5V)。六個(gè)反相器的輸入輸出引腳依次排列,例如1A(輸入)與1Y(輸出)構(gòu)成第一個(gè)反相器。

- 關(guān)鍵參數(shù):了解其電源電壓(典型值5V)、高低電平閾值電壓、傳輸延遲時(shí)間等,對(duì)于深入理解仿真結(jié)果很有幫助。

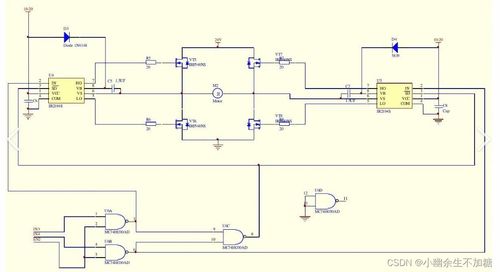

第二部分:仿真環(huán)境搭建(以Multisim為例)

- 創(chuàng)建新項(xiàng)目:?jiǎn)?dòng)Multisim,創(chuàng)建一個(gè)新的空白電路圖。

- 放置元件:

- 從元件庫(kù)中查找并放置74LS04。路徑通常為:"Place" -> "Component" -> 在"Group"中選擇"TTL" -> 在"Family"中選擇"74LS" -> 找到"74LS04D"(或類似型號(hào))。

- 放置電源:從"Sources"庫(kù)中放置一個(gè)"VCC"(設(shè)置為+5V)和一個(gè)"GROUND"。

- 放置輸入信號(hào)源:為了測(cè)試,我們可以使用一個(gè)數(shù)字時(shí)鐘信號(hào)源。從"Sources" -> "SIGNALVOLTAGESOURCES"中找到"CLOCK_VOLTAGE",將其頻率設(shè)置為1Hz(便于觀察),電壓幅值設(shè)置為5V。這模擬了一個(gè)在0V和5V之間周期性變化的輸入信號(hào)。

- 放置測(cè)量?jī)x器:從儀器工具欄中,拖拽一個(gè)"Oscilloscope"(示波器)到工作區(qū),用于觀察輸入和輸出的波形。

- 連接電路:

- 將VCC(5V)連接到74LS04的第14腳,GND連接到第7腳。

- 將時(shí)鐘信號(hào)源的正極連接到任一反相器的輸入端(如第1腳,1A),負(fù)極接地。

- 將該反相器的輸出端(第2腳,1Y)連接到示波器的一個(gè)通道(如A通道)。

- 將時(shí)鐘信號(hào)源的輸入端也連接到示波器的另一個(gè)通道(如B通道),以便對(duì)比輸入和輸出波形。

- 確保所有未使用的反相器輸入端接地或接VCC(通過(guò)一個(gè)上拉/下拉電阻,如1kΩ,或直接連接以避免懸空導(dǎo)致不確定狀態(tài)),這是TTL電路設(shè)計(jì)的好習(xí)慣。

第三部分:運(yùn)行仿真與結(jié)果分析

- 啟動(dòng)仿真:點(diǎn)擊運(yùn)行按鈕。電路將開始進(jìn)行實(shí)時(shí)仿真。

- 觀察示波器:雙擊打開示波器面板。您應(yīng)該能看到兩個(gè)波形:

- 通道B(輸入信號(hào)):一個(gè)標(biāo)準(zhǔn)的方波,在0V(邏輯0)和5V(邏輯1)之間交替。

- 通道A(輸出信號(hào)):同樣是一個(gè)方波,但其相位與輸入波形完全相反。當(dāng)輸入為5V高電平時(shí),輸出為接近0V的低電平;當(dāng)輸入為0V低電平時(shí),輸出為接近5V的高電平。這正是反相器的邏輯功能體現(xiàn)。

- 深入分析:

- 電壓值:注意觀察,輸出的高電平可能略低于5V(典型值約3.4V),低電平可能略高于0V(典型值約0.2V)。這是TTL電路的特性,仿真結(jié)果會(huì)精確反映這一點(diǎn)。

- 傳輸延遲:如果您放大波形的時(shí)間軸,可能會(huì)觀察到輸出波形的邊沿(上升沿和下降沿)相對(duì)于輸入波形有一個(gè)微小的延遲(納秒級(jí))。這是門電路的固有傳輸延遲,仿真模型會(huì)包含這一特性。

第四部分:進(jìn)階仿真實(shí)驗(yàn)建議

掌握了基本仿真后,可以進(jìn)行更多探索,深化對(duì)數(shù)字電路的理解:

- 多級(jí)連接:將一個(gè)反相器的輸出連接到下一個(gè)反相器的輸入,構(gòu)成兩級(jí)反相。用示波器觀察,最終輸出波形應(yīng)與原始輸入波形同相,但經(jīng)歷了兩次延遲。

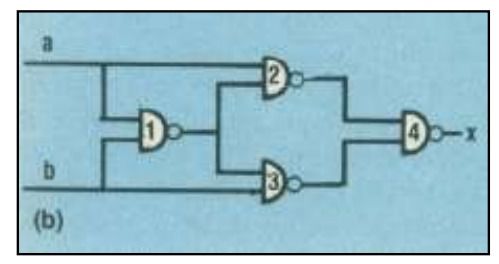

- 構(gòu)建簡(jiǎn)單邏輯電路:利用74LS04與其他基本門電路(如74LS08與門、74LS32或門)相結(jié)合,仿真一個(gè)簡(jiǎn)單的組合邏輯電路,例如

Y = !(A & B)(與非門功能,可由與門后接反相器實(shí)現(xiàn))。 - 測(cè)量動(dòng)態(tài)參數(shù):使用更精細(xì)的瞬態(tài)分析工具,精確測(cè)量輸出從低到高(tPLH)和從高到低(tPHL)的傳播延遲時(shí)間,并與芯片數(shù)據(jù)手冊(cè)進(jìn)行對(duì)比。

- 電源電壓影響:嘗試輕微改變VCC電壓(例如從4.75V到5.25V),觀察輸出電平的變化,理解電源電壓對(duì)TTL邏輯電平的影響。

###

通過(guò)這個(gè)基于74LS04的仿真教程,我們不僅驗(yàn)證了反相器的基本邏輯功能,還初步掌握了數(shù)字電路仿真的核心流程:選擇元件、搭建電路、設(shè)置激勵(lì)、運(yùn)行仿真、分析結(jié)果。仿真技術(shù)是現(xiàn)代集成電路和數(shù)字系統(tǒng)設(shè)計(jì)不可或缺的工具。希望本教程能成為您踏入數(shù)字邏輯設(shè)計(jì)殿堂的第一塊穩(wěn)固基石,鼓勵(lì)您繼續(xù)探索更復(fù)雜的門電路、時(shí)序電路乃至大規(guī)模數(shù)字系統(tǒng)的仿真與設(shè)計(jì)。記住,實(shí)踐出真知,多動(dòng)手嘗試不同的電路連接和測(cè)試方案,是提升設(shè)計(jì)能力的最佳途徑。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.cmabbio.com.cn/product/83.html

更新時(shí)間:2026-04-14 18:43:07